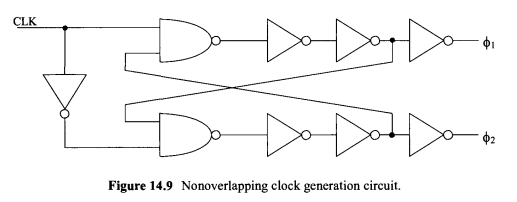

NOTES ON 2-PHASE NON OVERLAPPING CLOCK GENERATORS The dynamic shift register used in the baseline ELEC4609 project requires 2-ph

NOTES ON 2-PHASE NON OVERLAPPING CLOCK GENERATORS The dynamic shift register used in the baseline ELEC4609 project requires 2-ph

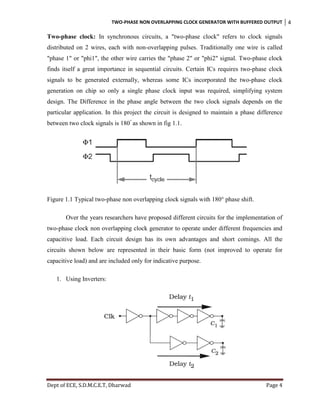

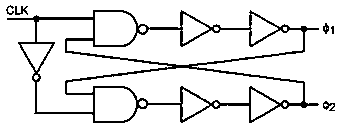

NOTES ON 2-PHASE NON OVERLAPPING CLOCK GENERATORS The dynamic shift register used in the baseline ELEC4609 project requires 2-ph

Sensors | Free Full-Text | T/R RF Switch with 150 ns Switching Time and over 100 dBc IMD for Wideband Mobile Applications in Thick Oxide SOI Process

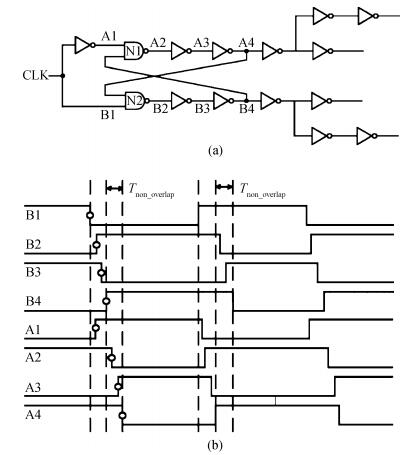

Example of a commonly used two-phase non-overlapping clock generator... | Download Scientific Diagram

Phase locked loop-based clock synthesizer for reconfigurable analog-to-digital converters | Analog Integrated Circuits and Signal Processing

Example of a commonly used two-phase non-overlapping clock generator... | Download Scientific Diagram

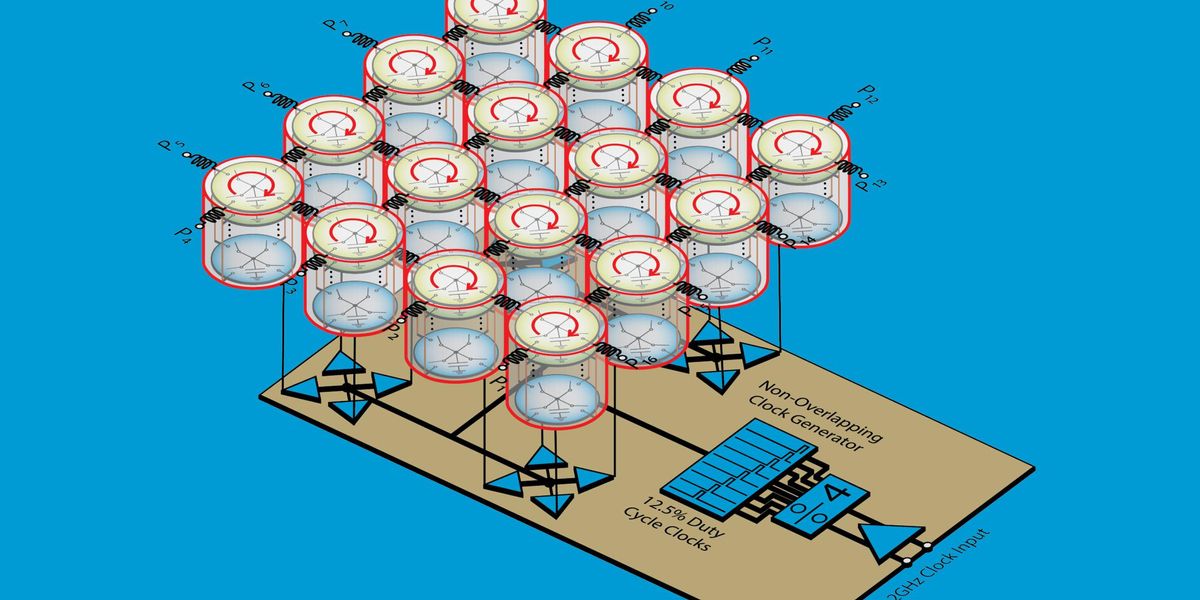

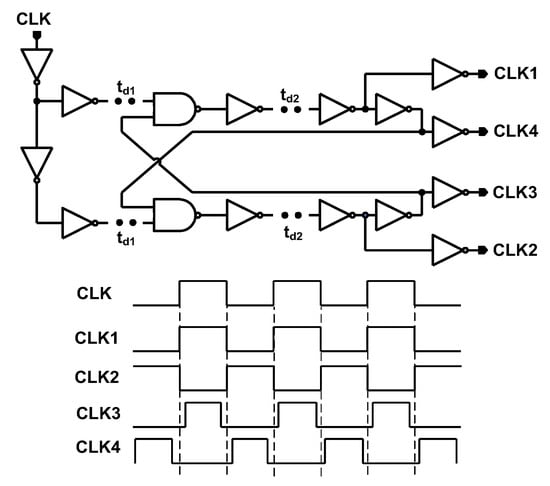

A generalized timing-skew-free, multi-phase clock generation platform for parallel sampled-data systems - Circuits and Systems,

Nonoverlapping Clock Generator with Optimized Falling/Rising EDGE Delay for Analog to Digital....... - YouTube